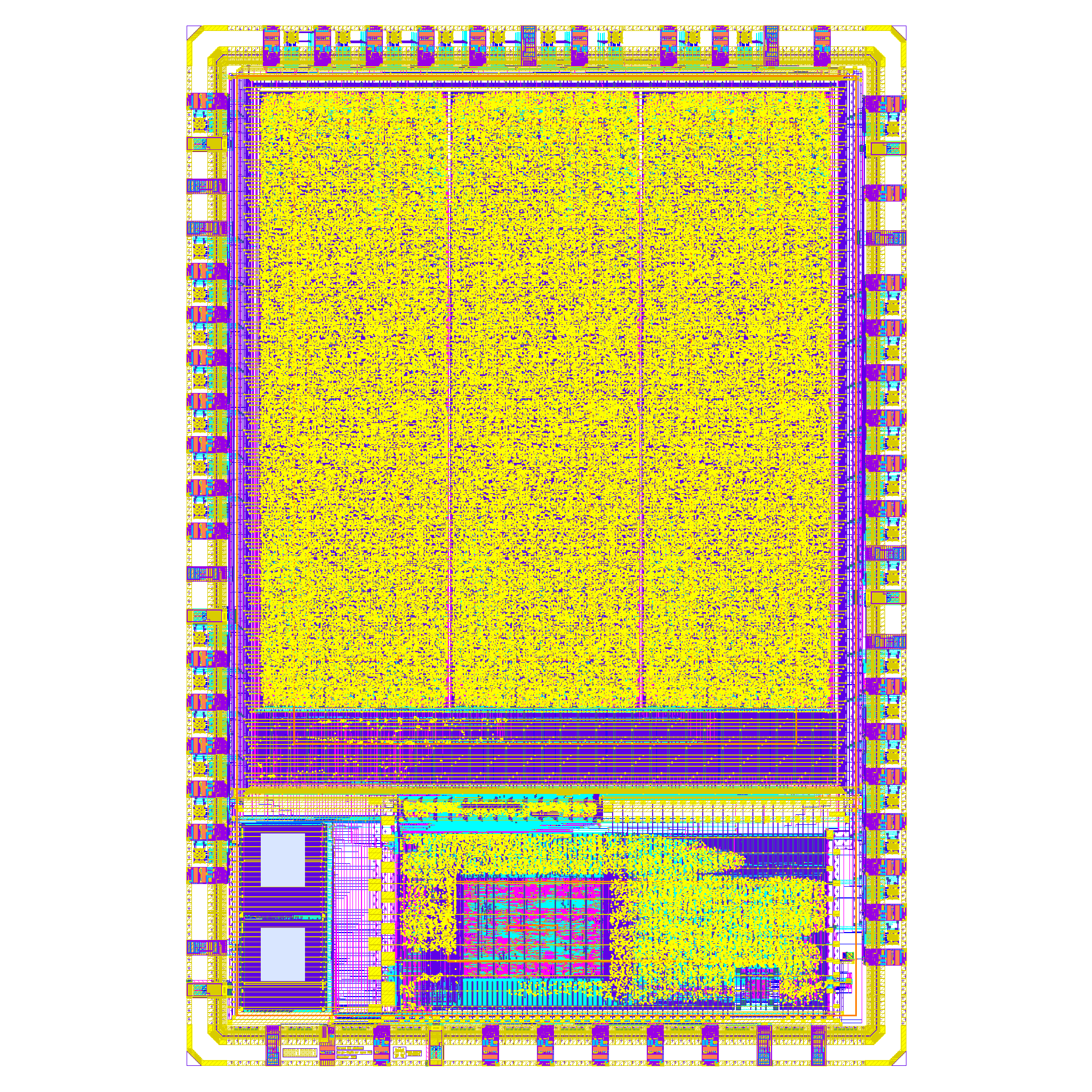

Caravel management SoC attached to the largest possible DFFRAM that can fit the user's area. For the RAM related development, refer to DFFRAM

The DFFRAM macro is placed on the management area wishbone bus at address (0x30000000). For the memory interface and wishbone bus conversion, refer to Caravel_RAM_24KB_wb

MGMT-WB | DFFRAM | Description | ----------------- | ------------- | ------------- | wb_adr_i[14:2] | A | Address | wb_dat_i | Di | Input Data | wb_sel_i & wb_we_i | WE | Write-Enable | wb_cyc_i & wb_stb_i | EN | Enable | wb_dat_o | Do | Output Data

Developed a 16bit processor having its own Reduced Instruction Set with least possible number of instructions in it such that the designed Processor can be used to implement almost any Function. The Developed IC can be used to understand mirco-architecture of a processor by students.

1.00

sky130A